#

# Tunnel Field-Effect Transistors Based on InP-GaAs Heterostructure Nanowires

Bahram Ganjipour,\* Jesper Wallentin, Magnus T. Borgström, Lars Samuelson, and Claes Thelander

Division of Solid State Physics, Lund University, Box 118, S-22100, Lund, Sweden

he tunnel field-effect transistor (TFET) belongs to the family of so-called steep-slope devices that are currently being investigated for ultra-low-power electronic applications.<sup>1-3</sup> The concept has been explored in several material systems based on semiconductor *p-i-n* junctions,<sup>4–7</sup> carbon nanotubes,8 and semiconductor nanowires.<sup>9–12</sup> A key feature of the TFET, which is critical for low-power switching, is the possibility for an inverse subthreshold slope, S, below the limit of 60 mV/dec for normal FETs.<sup>4,8</sup> The fundamental challenge for realizing commercially competitive TFETs is a limited on-current level, which is typically addressed by creating higher doping levels and abrupt doping profiles. However, this may negatively affect the off-state properties due to a pronounced Urbach tail in the density of states, with a high density of impurity levels in the band gap.<sup>13</sup>

Some heterostructures offer a staggered band alignment, allowing a steeper band structure profile over the junction than that achievable by using doping modulation only. Such structures are currently being investigated as a means to boost TFET performance.<sup>14,15</sup> Additionally, using a smaller band gap material in the source is predicted to significantly enhance the tunnel current.<sup>16</sup> In this respect, the III-V semiconductors are highly interesting, as they typically have low effective carrier masses and, in contrast to Si and Ge, direct band gaps that allow for efficient tunneling.<sup>17</sup> A few special heterostructures, such as InAs and GaSb, even have broken band lineups, whereby the band-to-band transport occurs without any barrier.12,18,19

Semiconductor nanowires are particularly attractive for TFET research, as they allow for heteroepitaxy of lattice mismatched materials, and the geometry of the structure also facilitates wrap-gate formation to the active region of the device.<sup>20</sup>

### ABSTRACT

We present tunneling field-effect transistors fabricated from InP-GaAs heterostructure nanowires with an *n-i-p* doping profile, where the intrinsic InP region is modulated by a top gate. The devices show an inverse subthreshold slope down to 50 mV/dec averaged over two decades with an on/off current ratio of approximately  $10^7$  for a gate voltage swing ( $V_{GS}$ ) of 1 V and an on-current of 2.2  $\mu$ A/ $\mu$ m. Low-temperature measurements suggest a mechanism of trap-assisted tunneling, possibly explained by a narrow band gap segment of InGaAsP.

KEYWORDS: nanowire · tunnel transistor · heterostructure · InP · GaAs · MOSFET

For nanowires scaled to the 1D transport regime, the TFET device properties are also believed to be improved,<sup>14</sup> however, under the assumption that the surface properties can be controlled. Recent developments in nanowire growth and doping control have allowed studies of band-to-band tunneling in Si nanowires,<sup>9,10</sup> in InP-GaAs heterostructure nanowires,<sup>21</sup> and in bulk Si to InAs nanowire interfaces.<sup>15</sup> However, considerable work is still required to realize competitive nanowire-based TFETs, and many questions regarding the actual tunnel mechanism in such devices are not fully answered.

In this work we have studied the reverse bias properties of heterostructure InP  $(n^+-i)$ -GaAs  $(p^+)$  nanowires. The nanowires (NWs) were processed into TFETs by aligning omega-shaped top gates to the intrinsic InP segments, and source and drain contacts to the n/p segments. In reverse bias, the

\* Address correspondence to bahram.ganjipour@ftf.lth.se.

Received for review December 10, 2011 and accepted March 5, 2012.

Published online March 13, 2012 10.1021/nn204838m

© 2012 American Chemical Society

VOL.6 • NO.4 • 3109-3113 • 2012

JAI

www.acsnano.org

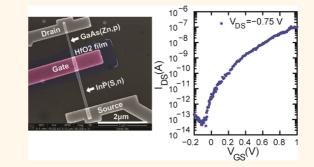

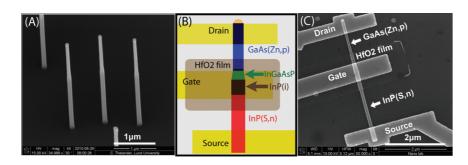

Figure 1. (A) SEM image of as-grown nanowires (30° tilt). (B) Schematic diagram of the InP-GaAs NW-TFET. (C) SEM top view of a fabricated device.

transistors show a band-to-band tunneling current up to 100 nA at  $V_{DS} = -0.75$  V (1.1  $\mu$ A/ $\mu$ m) with an on/off current ratio ( $I_{ON}/I_{OFF}$ ) of approximately 10<sup>7</sup> for a  $V_{GS}$ swing of 1 V. We find that both on-current and subthreshold slope are improved compared to previously reported nanowire TFETs based on epitaxially grown nanowires.<sup>9,10</sup> A minimum inverse subthreshold slope of around 50 mV/dec was observed close to pinch-off, averaged over a gate voltage range of 100 mV (two decades). The temperature dependence of the transfer characteristics indicates that the tunneling current consists of a trap-assisted tunneling (TAT) component and a band-to-band tunneling (BTBT) component.

### **RESULTS AND DISCUSSION**

A SEM micrograph of as-grown nanowires is shown in Figure 1A. The epitaxial growth resulted in nanowires about 4  $\mu$ m long, with roughly 2.5  $\mu$ m long InP sections (100 nm diameter) and 1.5  $\mu$ m long GaAs sections (85 nm diameter). The nominally intrinsic InP segment had a length of 200–300 nm. As a result of metallurgical interactions of the growth species with the Au seed particle when switching both group III and V elements simultaneously, a segment of narrow band gap InGaAsP is formed in the heterostructure region. This was observed by Wallentin *et al.* in the growth of corresponding tunnel diode structures and was suggested to contribute to the high band-to-band tunnel current density obtained for such diodes.<sup>21</sup> The In-GaAsP region is seen as the tapered region in Figure 1A.

SEM image of a fabricated device with an aligned top gate that covers the intrinsic InP region, and the transition region is shown in Figure 1C.

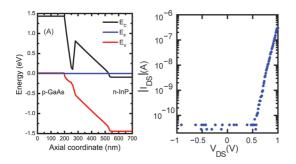

A schematic band diagram of an InP-GaAs heterostructure is shown in Figure 2A, based on the material composition and estimated doping levels discussed in ref 21 (*n*-InP:  $3 \times 10^{18}$  cm<sup>-3</sup>, *i*-InP:  $1 \times 10^{15}$  cm<sup>-3</sup>, *p*-GaAs:  $1 \times 10^{19}$  cm<sup>-3</sup>). The band diagram was created using a Poisson solver<sup>22</sup> with band offsets as reported by Pistol and Pryor.<sup>23</sup>

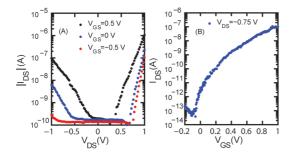

Electrical measurements were performed on individual devices under vacuum and dark conditions at room temperature. In all  $n^+$ -*i*- $p^+$  devices the *n*-side was grounded and the drain voltage,  $V_{DS}$ , was applied to the *p*-side. The diode  $I_{DS} - V_{DS}$  curve of a heterostructure nanowire with no fabricated gate is shown in Figure 2B. As no gate is present, the applied voltage at reverse bias drops over both the heterostructure and the intrinsic region of the nominally undoped InP segment, thus not giving conditions for BTBT. The corresponding  $I_{DS} - V_{DS}$  output characteristics of a 3-terminal (top-gated) device are shown in Figure 3A. As a result of the device design, the top gate was observed to affect both the reverse and the forward current levels. For a reverse (negative)  $V_{DS}$ , a positive gate voltage ( $V_{GS}$ ) is used to shift the conduction band of the InP-i segment in such a way that band-to-band tunneling is possible. In the case of a positive (forward)  $V_{\rm DS}$ , an applied gate voltage leads to electron accumulation or depletion on the InP side of the junction. For negative  $V_{GS}$  the InP (i)-segment becomes depleted, which extends the depletion region and prevents band-to-band tunneling. Instead the device behaves like a rectifying *p*-*n* junction, where the negative gate bias increases the reverse breakdown current and lowers the ideality factor in the forward direction. The onset voltage approaches that of an ideal diode, i.e., the band gap minus the InP-GaAs band offset. For positive  $V_{GS}$  we observed a similar onset of forward current ( $V_{DS} = 0.25$  V), as in the case of the heavily doped  $n^+-p^+$  diode studied,<sup>21</sup> although in this case without the region of negative differential resistance.

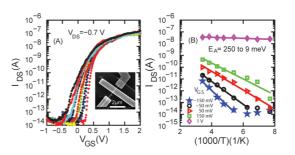

Figure 3B depicts the measured transfer characteristics of a fabricated device under reverse bias ( $V_{DS}$  = -0.75 V). We explain the strong dependence of  $I_{DS}$  on  $V_{GS}$  by band-to-band tunneling, where the tunneling probability increases for increasing positive V<sub>GS</sub>. An on/ off current ratio close to  $10^7$  was observed at  $V_{DS}$  = -0.75 V for a V<sub>GS</sub> swing of 1 V. For the same device at  $V_{\rm DS} = -0.85$  V and  $V_{\rm GS} = 1$  V, an on-current of 2.2  $\mu$ A/ $\mu$ m was obtained. At  $V_{DS} = -0.75$  V, a minimum inverse subthreshold slope,  $S = -[d(\log 10 I_{DS})/dV_{GS}]^{-1}$ , of 50 mV/dec was observed close to pinch-off, where the slope was averaged over a range of 100 mV in gate voltage (Figure 3B). This value is below the  $k_{\rm B}T \ln$  $10/q \approx 60$  mV/dec subthreshold slope limit of conventional Metal-Oxide Semiconductor Field-Effect Transistor (MOSFET) ( $k_{\rm B}$ , T, and q are the Boltzmann constant,

VOL.6 • NO.4 • 3109-3113 • 2012

agnanc www.acsnano.org

Figure 2. (A) Modeled energy band diagram of the nanowire with  $p^+$ -*i*- $n^+$  doping profile. (B)  $I_{DS}-V_{DS}$  of a twoterminal device before top-gate fabrication, based on a *p*-*i*-*n* heterostructure nanowire.

Figure 3. (A) Absolute value of  $I_{DS}$  vs  $V_{DS}$  of a fabricated device at three different  $V_{GS}$  of -0.5, 0, and 0.5 V. (B) Transfer characteristics of a device for a reverse bias of  $V_{DS} = -0.75$  V.

the temperature, and the charge, respectively).<sup>24</sup> However, our measurements showed a distribution in inverse subthreshold slope between devices from 50 to 80 mV/dec. The average slope for  $V_{GS} = 0$  to 1 V was 150 mV/dec, which is an improvement compared to other reported nanowire tunnel FET concepts based on epitaxially grown NWs.<sup>9,10</sup> The low *S* demonstrates an excellent gate control, which indicates a surprisingly high-quality interface between InP and HfO<sub>2</sub> for the process conditions used. Recently, our group has demonstrated regular NW-FETs with *S* close to the thermal limits, which were also based on omega-gated InP NWs.<sup>25</sup>

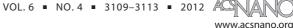

The temperature dependence of the subthreshold slope is a useful probe to investigate possible transport mechanisms contributing to the observed reversebiased transfer characteristics.<sup>7,8,10</sup> For this reason,  $I_{DS} - V_{GS}$  measurements were performed at different temperatures for  $V_{DS} = -0.7$  V for the device shown in the inset of Figure 4. Figure 4A depicts the transfer characteristics of a fabricated device at different temperatures between 100 and 300 K in steps of 20 K. Three regions with different  $V_{GS}$  dependence can be identified corresponding to onset of various transport mechanisms. At the OFF state (negative  $V_{GS}$ ) the main transport mechanism is Schockley-Read-Hall recombination in a reverse biased  $p^+$ -*i*- $n^+$  diode, which should be strongly temperature dependent. However, as the OFF current ( $I_{OFF}$ ) was close to the instrument sensitivity limits already at room temperature, such a temperature dependence could not be confirmed.

Figure 4. (A) Transfer characteristics for reverse bias  $V_{DS} = -0.7$  V at temperatures ranging from 100 to 300 K in steps of 20 K. For  $V_{GS} < 0.4$  V the subthreshold current is strongly temperature dependent. However, at higher gate voltage the drain current is temperature independent, confirming the presence of direct BTBT. Inset: SEM image of the corresponding device (NWs grown with 40 nm Au particle). (B) Arrhenius plots of TFET extracted at  $V_{DS} = -0.70$  V for different gate voltages. The extracted activation energies indicate that transport mechanisms are driven by TAT and direct BTBT at the low and high gate bias, respectively.

For 100 K < T < 300 K and intermediate gate bias  $(V_{GS} < 0.4 \text{ V})$  a strong temperature dependence of the drain current was observed. The strong temperature dependence cannot be explained only with a change in band gap and band offset with temperature. Similar device behavior has been reported by others,<sup>7,10</sup> in which case trap-assisted tunneling was proposed as a possible transport mechanism, where electrons first tunnel into a trap within the band gap, from which they are thermally excited into the conduction band. In our case, the narrow band gap section of InGaAsP as observed by X-ray energy dispersive spectroscopy may act as a trap for the electrons at low temperatures, thereby improving the subthreshold properties. Such a trap-assisted tunneling mechanism is supported by the results of Arrhenius plots made for different gate voltages (Figure 4B) where an activation energy of 0.25 eV is extracted for the subthreshold region ( $V_{GS} = -0.15$  V). A possible future study, aimed at verifying this interpretation, could be based on InAs-GaAs heterostructure nanowires, for which the narrow band gap section is completely eliminated.

The temperature dependence observed in this region may also be explained by band tailing associated with high doping levels,<sup>26</sup> known from studies of optical properties of III–V semiconductors, such as GaAs.<sup>27,28</sup> Such states may extend to energies within the band gap, resulting in an exponential extension of the density of states in the below band-edge region. The slope of the so-called Urbach tail, which is the exponential part of the absorption edge, may therefore be one explanation for the temperature dependence of the subthreshold region observed here. However, further studies are necessary to confirm this interpretation.

For  $V_{GS} > 0.5$  V (ON state), only a very weak temperature dependence of the drain current is observed. An activation energy of 9 meV is extracted at  $V_{GS} = 1$  V, confirming the presence of direct band-to-band tunneling in the device at higher gate voltages.

VOL.6 • NO.4 • 3109-3113 • 2012

JAr

www.acsnano.org

A few devices with a variation in gate—heterojunction overlap were fabricated. Here we found that in cases where the gate did not cover the entire tapered region (gate—drain underlap) the inverse subthreshold slope was degraded. As expected, gate control of the InGaAsP transition region appears critical to the device performance (see Supporting Information).

## CONCLUSIONS

We have demonstrated single nanowire InP-GaAs tunneling FETs with minimum *S* of 50 mV/dec and  $I_{ON}/I_{OFF}$  of 10<sup>7</sup>. A strong temperature dependence of

the subthreshold current indicates trap-assisted tunneling and thermal emission from traps. For positive gate voltages the temperature dependence is found to be considerably weaker, indicating direct band-to-band tunneling. These results demonstrate the versatility of III–V NW heterostructures as building blocks in future low-power electronics. It is expected that the TFET performance could be further enhanced with reduced diameters, with optimized doping profile, and by designing gates that fully wrap around the intrinsic device region.

### **METHODS**

Samples were prepared for nanowire growth by depositing 40 and 80 nm Au particles in a density of  $0.2 \,\mu m^{-2}$  on InP (111)B substrates by an aerosol technique.<sup>29</sup> The nanowires were grown in a low-pressure (100 mbar) metal organic vapor phase epitaxy system with a total flow of 6 L/min using hydrogen  $(H_2)$ as carrier gas. For InP growth, trimethylindium (TMI) and phosphine (PH<sub>3</sub>) were used as precursors, with constant molar fractions of  $\chi_{TMI} = 3.5 \times 10^{-6}$  and  $\chi_{PH3} = 6.25 \times 10^{-3}$ . Hydrogen sulfide ( $H_2S$ ) was added as *n*-type doping precursor<sup>30</sup> at a molar fraction of  $\chi_{H2S} = 7.1 \times 10^{-6}$ . For the GaAs section, trimethylgallium (TMG) and arsine (AsH $_3$ ) were used at molar fractions of  $\chi_{TMG} = 5.2 \times 10^{-6}$  and  $\chi_{AsH3} = 0.55 \times 10^{-3}$ . DEZn was here used as a GaAs NW *p*-dopant precursor<sup>31</sup> in a molar fraction of  $\chi_{DEZn} =$  $2.9 \times 10^{-7}$ . Finally, hydrogen chloride (HCl) at a molar fraction of  $\chi_{HCl} = 15.0 \times 10^{-6}$  was used to control the radial growth.<sup>32</sup> The samples were first annealed at 550 °C for 10 min under a PH<sub>3</sub>/H<sub>2</sub> gas mixture to desorb any surface oxides. The reactor was then cooled to a temperature of 420 °C, at which point growth was initiated by adding TMI. After a 15 s nucleation time, HCl and  $H_2S$ were added, after which n-type InP growth was continued for 9 min. Then H<sub>2</sub>S was switched off and one minute of nominally intrinsic InP was grown. GaAs growth was initiated by simultaneously switching group III, group V, and dopant precursors. After 10 min, growth was interrupted and the sample was cooled in a PH<sub>3</sub>/H<sub>2</sub> gas mixture.

After growth, nanowires were broken off and transferred to doped Si samples capped with a 100 nm thick SiO<sub>2</sub> thermal oxide. The locations of selected nanowires were then determined relative to predefined metal markers using a scanning electron microscope. The samples were spin-coated in Poly-MethylMethAcrylate (PMMA), followed by electron beam lithography exposure of a window that was aligned to the InP(*i*) segment and partially overlapping InP( $n^+$ ) and GaAs( $p^+$ ) segments. A high- $\kappa$  HfO<sub>2</sub> film was formed by atomic layer deposition of Tetrakis[DiMethylAmino]Hafnium (TDMAHf) and H<sub>2</sub>O at 100 °C, followed by lift-off. Gate and contact to  $n^+$ -type InP were fabricated in a single EBL step, where the InP segments were etched with H<sub>3</sub>PO<sub>4</sub>/H<sub>2</sub>O (1:9) for 2 min and then with H<sub>2</sub>SO<sub>4</sub>/H<sub>2</sub>O (1:3) for 1 min, followed by sulfur passivation for 10 min. A Ti/Au (20/80 nm) metal combination was used as the contact materials.

After another EBL step, the GaAs  $p^+$ -segments were etched in an HCl/H<sub>2</sub>O (1:1) solution for 10 s, followed by a 2 min surface passivation in an (NH<sub>4</sub>)<sub>2</sub>S<sub>X</sub> solution. A Pd/Zn/Pd (10/10/80 nm) metal combination, which is known to give ohmic contacts to p-GaAs NWs,<sup>21</sup> was used. Figure 1B and C show a schematic diagram and an SEM image of a fabricated device with an aligned top gate that covers the intrinsic InP region and the transition region (the tapered section).

*Conflict of Interest:* The authors declare no competing financial interest.

Acknowledgment. This work was conducted within the Nanometer Structure Consortium at Lund University (nmC@LU), with financial support from the Swedish Research

Council (VR), the Swedish Foundation for Strategic Research (SSF), and the Knut and Alice Wallenberg Foundation (KAW).

Supporting Information Available:  $I_{DS}-V_{DS}$  characteristics of two-terminal devices of InP and GaAs segments that show low-ohmic behavior, transfer characteristics of a device with gate –drain underlap, and gate leakage current. This material is available free of charge *via* the Internet at http://pubs.acs.org.

### **REFERENCES AND NOTES**

- Quinn, J. J.; Kawamoto, K.; McCombe, B. D. Subband Spectroscopy by Surface Channel Tunneling. *Surf. Sci.* 1978, 73, 190–196.

- 2. Baba, T. Proposal for Surface Tunnel Transistors. *Jpn. J. Appl. Phys.* **1992**, *31*, L455–L457.

- Kim, D.; Lee, Y.; Cai, J.; Lauer, I.; Chang, L.; Koester, S. J.; Sylvester., D.; Blaauw, D. Low Power Circuit Design Based on Heterojunction Tunneling Transistors in ISLPED. Proceedings of the 14thACM/IEEE International Symposium on Low Power Electronics and Design; ACM: New York, NY, USA, 2009; pp 219–224.

- Choi, W. Y.; Park, B. G.; Lee, J. D.; Lu, T.J. K. Tunneling Field-Effect Transistors (TFETs) with Subthreshold Swing (SS) Less Than 60 mV/dec. *IEEE Electron Device Lett.* 2007, 28, 743–745.

- Leonelli, D.; Vandooren, A.; Rooyackers, R.; Verhulst, A. S.; Gendt, S. D.; Heyns, M. M.; Groeseneken, G. Performance Enhancement in Multi Gate Tunneling Field Effect Transistors by Scaling the Fin-Width. *Jpn. J. Appl. Phys.* 2010, 49, 04DC10.

- Kazazis, D.; Jannaty, P.; Zaslavsky, A.; Le Royer, C.; Tabone, C.; Clavelier, L.; Cristoloveanu, S. Tunneling Field-Effect Transistor with Epitaxial Junction in Thin Germanium-on-Insulator. *Appl. Phys. Lett.* **2009**, *94*, 263508.

- Mookerjea, S.; Mohata, D.; Mayer, T.; Narayanan, V.; Datta, S. Temperature-Dependent *I-V* Characteristics of a Vertical In<sub>0.53</sub>Ga0.47As Tunnel FET. *IEEE Electron Device Lett.* 2010, 31, 564–566.

- Appenzeller, J.; Lin, Y. M.; Knoch, J.; Avouris, P. Band-to-Band Tunneling in Carbon Nanotube Field-Effect Transistors. *Phys. Rev. Lett.* **2004**, *93*, 196805.

- Björk, M. T.; Knoch, J.; Schmid, H.; Riel, H.; Riess, W. Silicon Nanowire Tunneling Field-Effect Transistors. *Appl. Phys. Lett.* 2008, 92, 193504.

- Vallett, A. L.; Minassian, S.; Kaszuba, P.; Datta, S.; Redwing, J. M.; Mayer, T. S. Fabrication and Characterization of Axially Doped Silicon Nanowire Tunnel Field-Effect Transistors. *Nano Lett.* **2010**, *10*, 4813–4818.

- Gandhi, R.; Chen, Z.; Singh, N.; Banerjee, K.; Lee, S. Vertical Si-Nanowire *n*-Type Tunneling FETs With Low Subthreshold Swing (≤ 50mV/decade) at Room Temperature. *IEEE Electron Device Lett.* **2011**, *32*, 437–439.

- Smith, J. T.; Sandow, C.; Das, S.; Minamisawa, R. A.; Mantl, S.; Appenzeller, J. Silicon Nanowire Tunneling Field-Effect

Transistor Arrays: Improving Subthreshold Performance Using Excimer Laser Annealing. *IEEE Trans. Electron Devices* **2011**, *58*, 1822–1829.

- Pankove, J. I. Optical Processes in Semiconductors; Dover Publications, Inc.: New York, 1975.

- Knoch, J.; Appenzeller, J. Modeling of High-Performance p-Type III–V Heterojunction Tunnel FETs. *IEEE Electron Device Lett.* 2010, *31*, 305–307.

- Björk, M. T.; Schmid, H.; Bessire, C. D.; Moselund, K. E.; Ghoneim, H.; Karg, S.; Lörtscher, E.; Riel, H. Si--InAs Heterojunction Esaki Tunnel Diodes with High Current Densities. *Appl. Phys. Lett.* **2010**, *97*, 163501.

- Verhulst, A. S.; Vandenberghe, W. G.; Maex, K.; De Gendt, S.; Heyns, M. M.; Groeseneken, G. . Complementary Silicon-Based Heterostructure Tunnel-FETs with High Tunnel Rates. *IEEE Electron Device Lett.* **2008**, *29*, 1398–1401.

- Ionescu, A. M.; Reil, H. Tunnel Field-Effect Transistors as Energy-Efficient Electronic Switches. *Nature* 2011, 479, 329–337.

- Borg, B. M.; Dick, K. A.; Ganjipour, B.; Pistol, M. E.; Wernersson, L. E.; Thelander, C. InAs/GaSb Heterostructure Nanowires for Tunnel Field-Effect Transistors. *Nano Lett.* 2010, 10, 4080–4085.

- Ganjipour, B.; Dey, A. W.; Borg, B. M.; Ek, M.; Pistol, M.-E.; Dick, K. A.; Wernersson, L.-E.; Thelander, C. High Current Density Esaki Tunnel Diodes Based on GaSb-InAsSb Heterostructure Nanowires. *Nano Lett.* **2011**, *11*, 4222–4226.

- Thelander, C.; Fröberg, L. E.; Rehnstedt, C.; Samuelson, L.; Wernersson, L. E. Vertical Enhancement-Mode InAs Nanowire Field-Effect Transistor with 50-nm Wrap Gate. *IEEE Electron Device Lett.* **2008**, *29*, 206–208.

- Wallentin, J.; Persson, J. M.; Wagner, J. B.; Samuelson, L.; Deppert, K.; Borgström, M. T. High-Performance Single Nanowire Tunnel Diodes. *Nano Lett.* **2010**, *10*, 974–979.

- Tan, I. H.; Snider, G. L.; Chang, L. D.; Hu, E. L. A Self-Consistent Solution of Schrödinger–Poisson Equations Using a Non-uniform Mesh. J. Appl. Phys. **1990**, 68, 4071–4076.

- Pistol, M. E.; Pryor, C. E. Band Structure of Segmented Semiconductor Nanowires. *Phys. Rev. B* 2009, *80*, 035316.

- 24. Sze, S. M. Physics of Semiconductor Devices; Wiley: New York, 1981.

- Storm, K.; Nylund, G.; Borgström, M. T.; Wallentin, J.; Fasth, C.; Thelander, C.; Samuelson, L. Gate-Induced Fermi Level Tuning in InP Nanowires at Efficiency Close to the Thermal Limit. *Nano Lett.* **2011**, *11*, 1127–1130.

- Abul-khayer, M.; Lake, R. K. Effects of Band-Tails on the Subthreshold Characteristics of Nanowire Band-to-Band Tunneling Transistors. J. Appl. Phys. 2011, 110, 074508.

- 27. Tuck, B. Conduction Band Density of States in Impure GaAs. J. Phys. Chem. Solids **1968**, 29, 615–622.

- Park, S.; Choe, B. Radiative Mechanisms and Transport Properties of GaAs:Si Light-Emitting Diodes. J. Korean Phys. Soc. 1989, 22, 62–66.

- Magnusson, M. H.; Deppert, K.; Malm, J. O.; Bovin, J. O.; Samuelson, L. Size-Selected Gold Nanoparticles by Aerosol Technology. *Nanostruct. Mater.* 1999, *12*, 45–48.

- Minot, E. D.; Kelkensberg, F.; vanKouwen, M.; vanDam, J. A.; Kouwenhoven, L. P.; Zwiller, V.; Borgström, M. T.; Wunnicke, O.; Verheijen, M. A.; Bakkers, E. P. A. M. Single Quantum Dot Nanowire LEDs. *Nano Lett.* **2007**, *7*, 367–371.

- Gutsche, C.; Regolin, I.; Blekker, K.; Lysov, A.; Prost, W.; Tegude, F. J. Controllable *p*-Type Doping of GaAs Nanowires During Vapor-Liquid-Solid Growth. *J. Appl. Phys.* 2009, 105, 024305.

- Borgström, M. T.; Wallentin, J.; Trägårdh, J.; Ramvall, P.; Ek, M.; Wallenberg, L. R.; Samuelson, L.; Deppert, K. *In Situ* Etching for Total Control Over Axial and Radial Nanowire Growth. *Nano Res.* 2010, *3*, 264–270.

www.acsnano.org